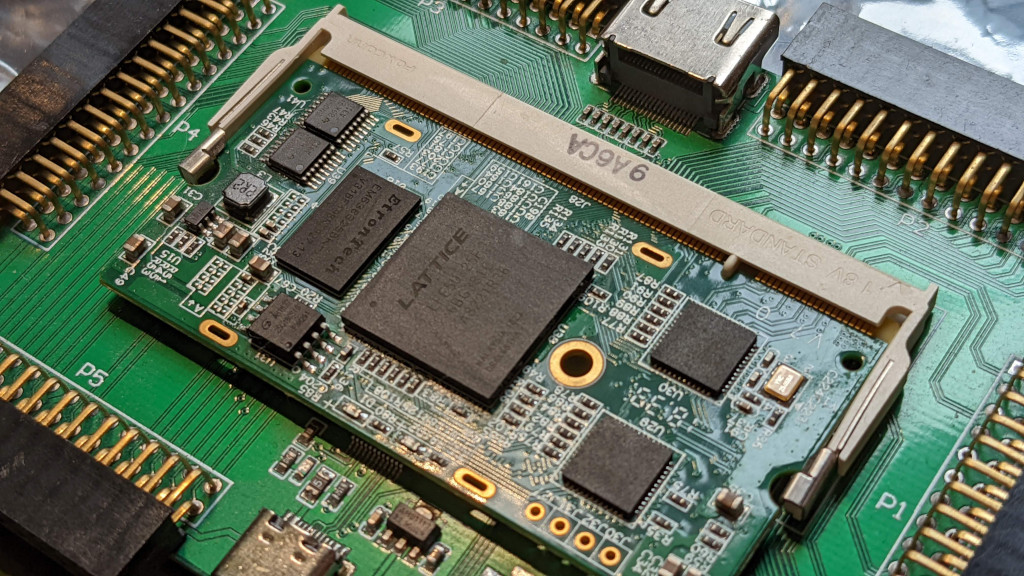

The pervious post on building the LED example is Firmware Testing and aims to add the building of the FPGA for the iceBreaker FPGA board. The FPGA image will be built using the github actions workflow that is similar to that which was used in my post but with the addition of adding some detailed comments in the pull requests and using the Lattice ice40 part in place of the Lattice ECP5.

The continuation of the pervious workflow starts by adding the tools for building the FPGA image in the form of yosys and nextpnr, which will be used. These are both installed using pip, as this is the quickest way to get upto date builds of the tools which can be installed quickly.

- name: Install deps

run: |

sudo -H pip3 install yowasp-yosys

sudo -H pip3 install yowasp-nextpnr-ice40-all

# Runs a set of commands using the runners shell

First up we are doing sythesis using yosys, this takes our verilog design and converts it into map RTL design which is mapped onto the logic cells that are in our FPGA. For this design we are using the default synth command for the ice40 device, and generating the local map as a json file, ready to be put though the place and route tool.

- name: Run yosys on the files

working-directory: project/PMod_LED/Firmware

run: |

yowasp-yosys -p 'synth_ice40 -top blinky -json blinky.json' blinky.v

The next step is to use nextpnr to place and route our design onto the ice40 FPGA, here we is where we want to collect the data on the designs performance, this is done by adding the --log nextpnr.log flag is the nextpnr. at this stage we also use icepack to prepare out design so it can be uploaded to our FPGA should we download it.

- name: Run nextpnr on the files

working-directory: project/PMod_LED/Firmware

run: |

yowasp-nextpnr-ice40 --up5k --package sg48 --json blinky.json --pcf icebreaker.pcf --asc blinky.asc --log nextpnr.log

yowasp-icepack blinky.asc blinky.bin

The next stage is to extract the data from nextpnr log file, using some command line tools to put the data from the log files into a text file called utilisation.txt before then formatting the text into the results.txt file.

- name: Extract the stats from the build log file

working-directory: project/PMod_LED/Firmware

run: |

echo 'Info: FPGA Place and Route statistics:' > utilisation.txt

echo 'Info:```' >> utilisation.txt

awk '/Info: Logic utilisation before packing:/' RS= nextpnr.log >> utilisation.txt

echo 'Info: ' >> utilisation.txt

awk '/Total DFFs:/' RS= nextpnr.log >> utilisation.txt

echo 'Info: ' >> utilisation.txt

awk '/Info: Device utilisation:/' RS= nextpnr.log >> utilisation.txt

echo 'Info: ' >> utilisation.txt

grep "MHz" nextpnr.log | tail -1 >> utilisation.txt

echo 'Info:```' >> utilisation.txt

sed 's/^.\{5\}//' utilisation.txt >results.txt

rm utilisation.txt

The data in the results.txt is then used to comment on the Pull request (Assuming the github action is not running on the scheduled event), to allow the build statistics including device utilization and the estimated maximum design frequency to be viewed in the pull request comments.

- name: comment PR

if: github.event.schedule != '0 8 * * 1'

uses: machine-learning-apps/pr-comment@master

env:

GITHUB_TOKEN: ${{ secrets.GITHUB_TOKEN }}

with:

path: project/PMod_LED/Firmware/results.txt

The generated values that are produced by next-pnr for the ice40 FPGA are then add added to the github pull request, so they can be veiwed.

Device utilisation:

ICESTORM_LC: 40/ 5280 0%

ICESTORM_RAM: 0/ 30 0%

SB_IO: 9/ 96 9%

SB_GB: 2/ 8 25%

ICESTORM_PLL: 0/ 1 0%

SB_WARMBOOT: 0/ 1 0%

ICESTORM_DSP: 0/ 8 0%

ICESTORM_HFOSC: 0/ 1 0%

ICESTORM_LFOSC: 0/ 1 0%

SB_I2C: 0/ 2 0%

SB_SPI: 0/ 2 0%

IO_I3C: 0/ 2 0%

SB_LEDDA_IP: 0/ 1 0%

SB_RGBA_DRV: 0/ 1 0%

ICESTORM_SPRAM: 0/ 4 0%

Max frequency for clock 'CLK$SB_IO_IN_$glb_clk': 74.76 MHz (PASS at 12.00 MHz)